みなさま、お疲れ様です。

少し前にフルブリッジコンバータの動作原理を解説して、シミュレーションで動作確認しました。

そのときの記事は以下です↓。良かったら読んでみて下さい。

1回目:【電源回路】フルブリッジコンバータの動作原理

2回目:【電源回路】フルブリッジコンバータの動作をシミュレーションで理解する

3回目:【電源回路】電圧モード制御フルブリッジコンバータの動作モデルを作った(本記事)

4回目:【電源回路】フルブリッジコンバータの伝達関数

5回目:【電源回路】電流モード制御フルブリッジコンバータの動作モデルを作った

今回はフィードバック制御部分を追加して、とりあえずDUTYを自分で計算して動いてくれる回路モデルをPspice for TIで作りました。

動作条件は以下の通りです。

| 項目 | 値 |

|---|---|

| 入力電圧 | 140[V] |

| 出力電圧 | 12[V] |

| スイッチング周波数 | 10[kHz] |

| 制御モード | 電圧モード制御 |

ということでその内容を記事にしようと思います。はい。

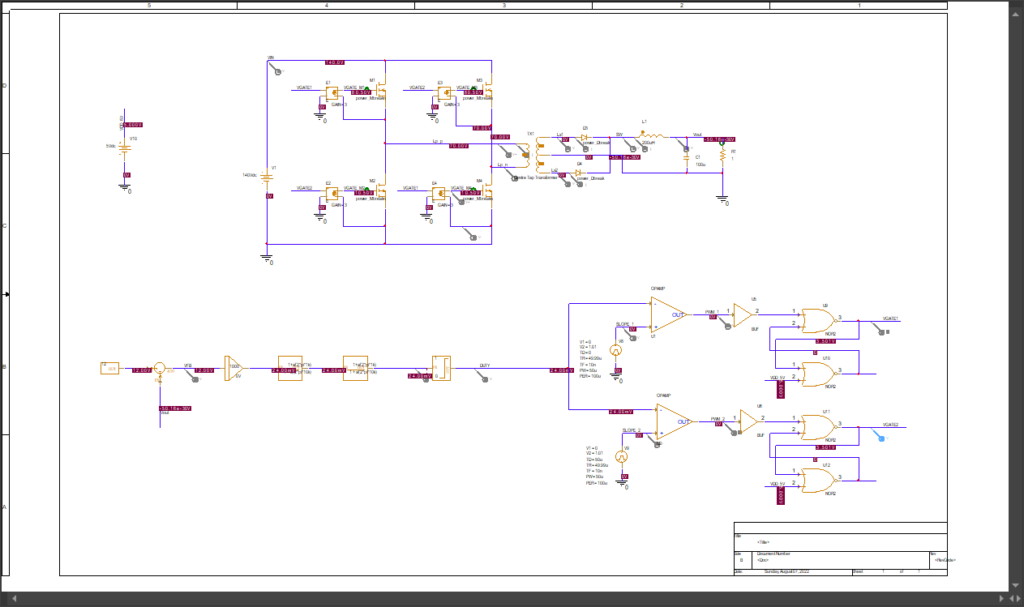

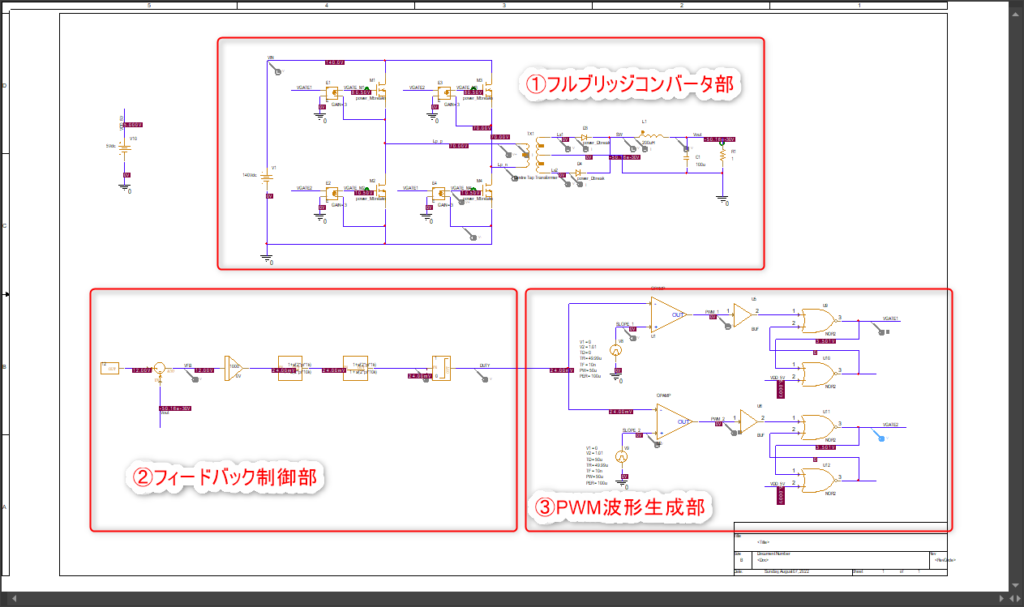

まずは回路全体

回路の全体像は以下のようになります↓。

意外と回路規模は少ないですね。理想素子だらけなんで現実的とは言い難いです。あくまでビヘイビア(=動作)モデルです。ここから実在する部品へ落とし込んでいくってのが、実際の設計になるんでしょうね。

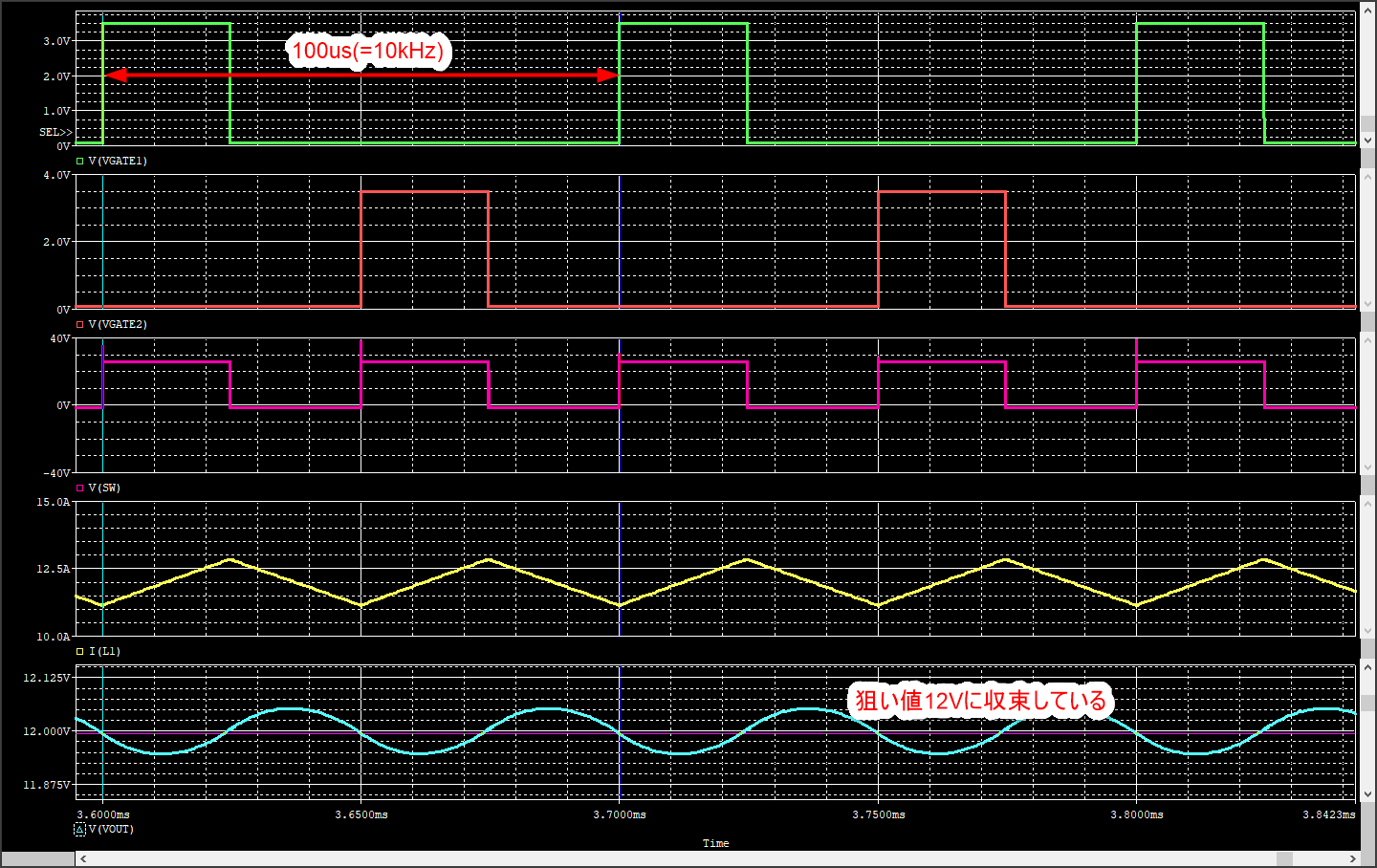

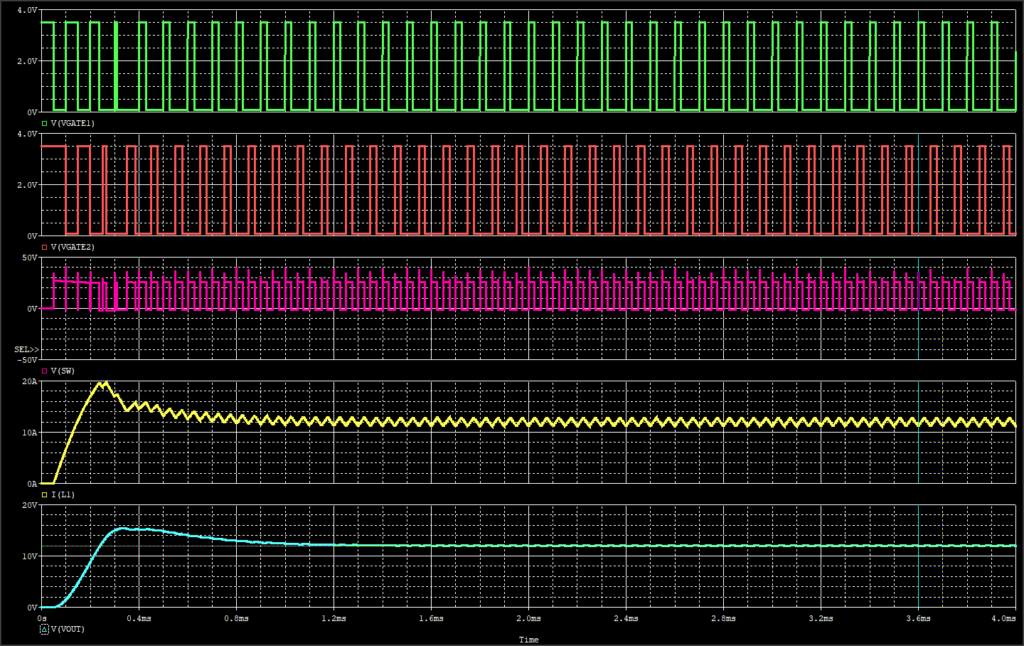

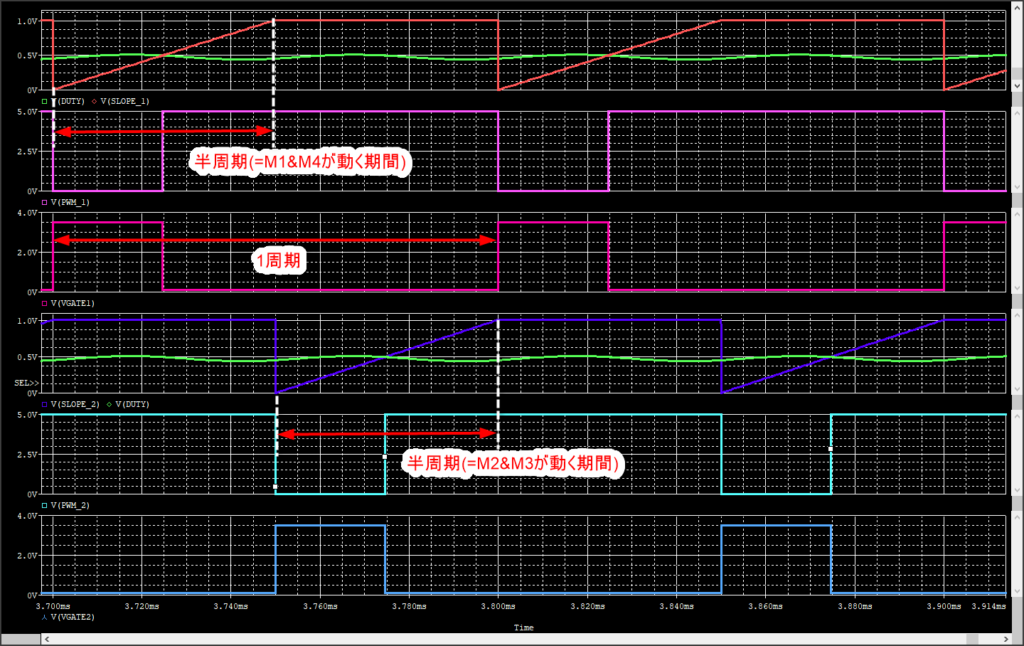

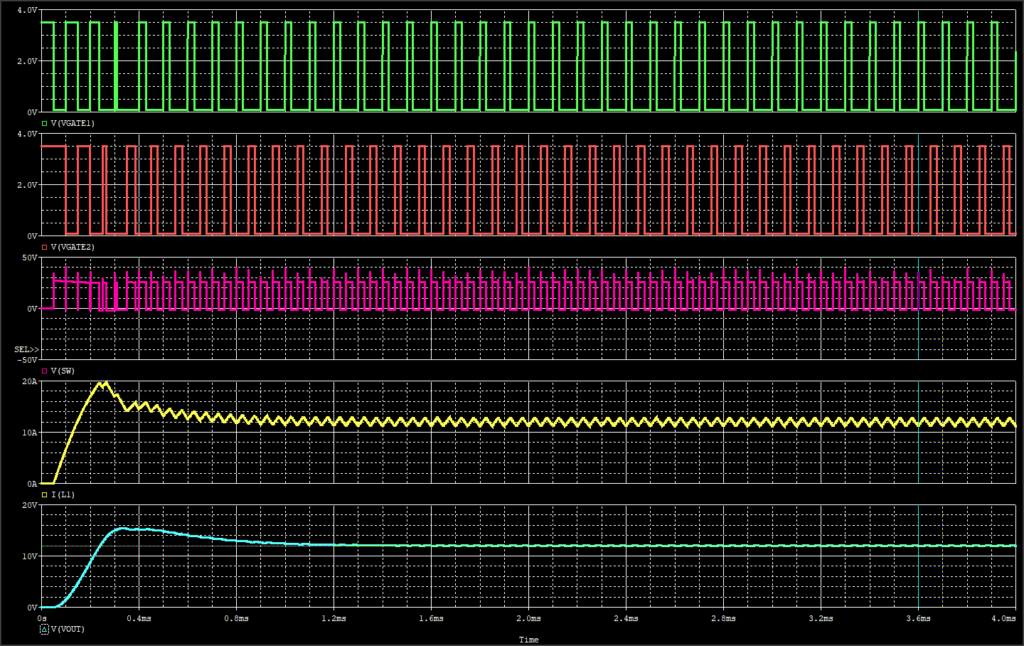

ちなみに動作波形は以下のようになります。

上から

VGATE1:M1,M4のゲート電圧

VGATE2:M2,M3のゲート電圧

VSW:スイッチング電圧(出力コイルの左端電圧)

IL:出力コイル電流

Vout:出力電圧

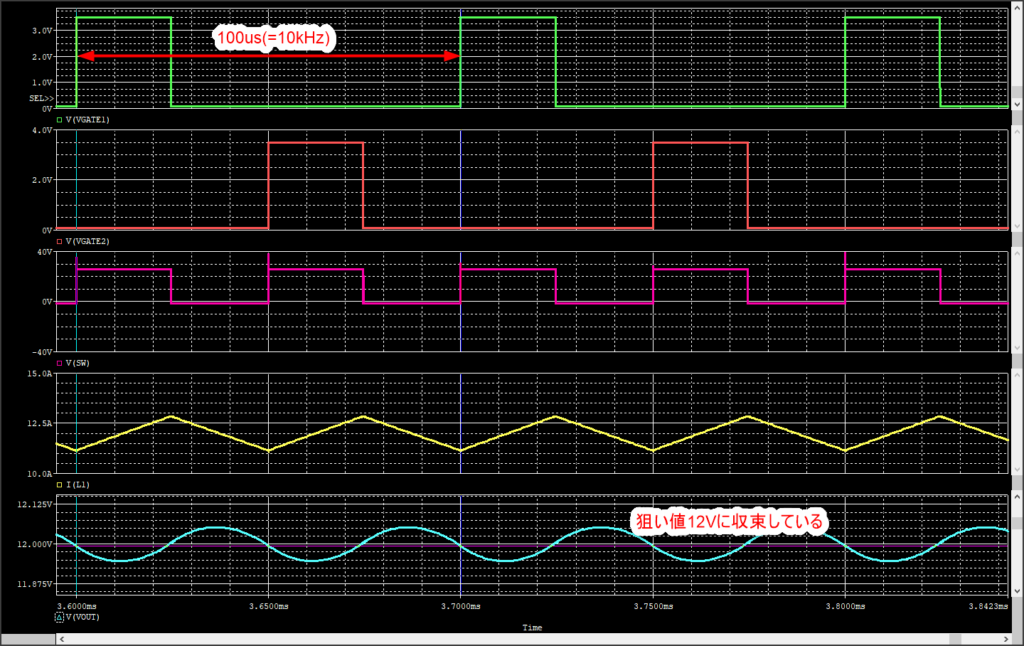

拡大波形↓。

ちゃんと狙いの出力電圧12Vに収束しています。スイッチング波形の乱れもなし。

問題なしです。

ちなみに最初に出力電圧がオーバーシュートしているのはしゃーないです。ソフトスタート機能を付けてないからです。

結構適当に設定したのですが、一旦動いてくれて一安心です。以下では何を考えて、どこをどう設定したのかを解説したいと思います。

3つの機能ブロックから構成されている

今回の動作モデルは3つの機能ブロックから構成されています。

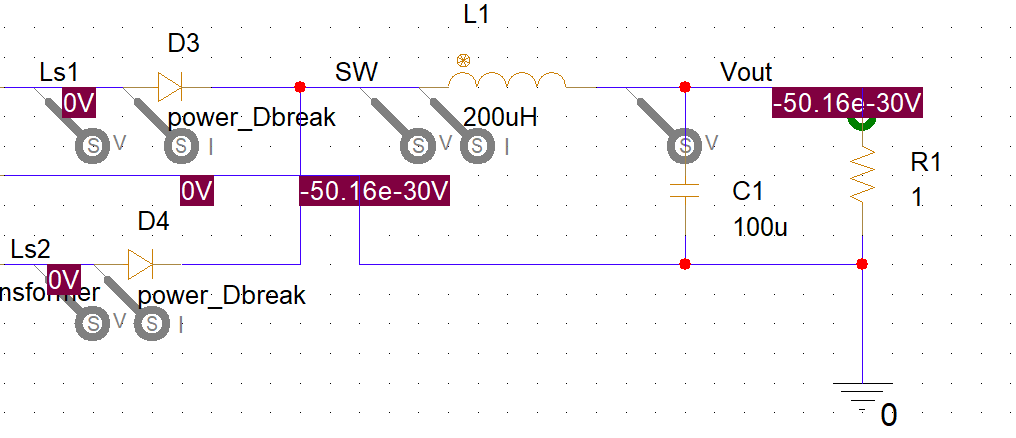

フルブリッジコンバータ部(メイン)

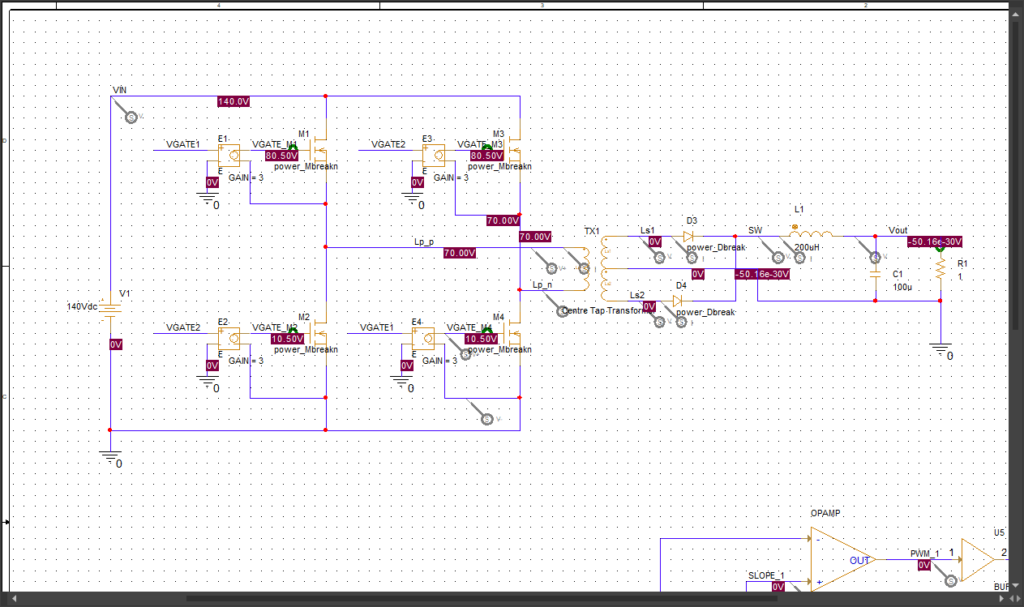

こんな感じですね↓。

前回の記事(2回目)で動作確認してからほとんど変化はありません。狙いの動作も前回の記事(1回目)で説明した通りです。

M1~M4のスイッチMOSFETのゲート電圧を与えるために電圧制御電圧源を付けています。PWM生成部で生成されたゲート波形を電圧に直してスイッチのゲートに与えるために付けています。

まぁそんだけですね。

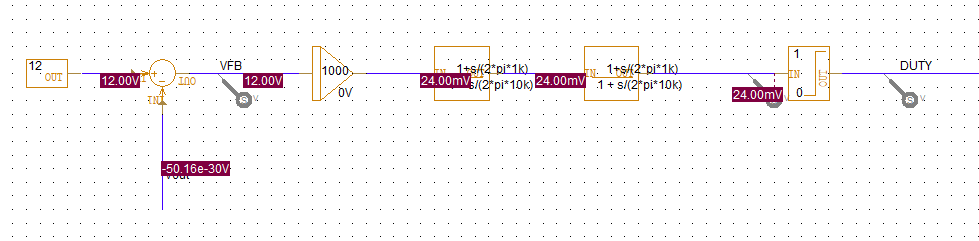

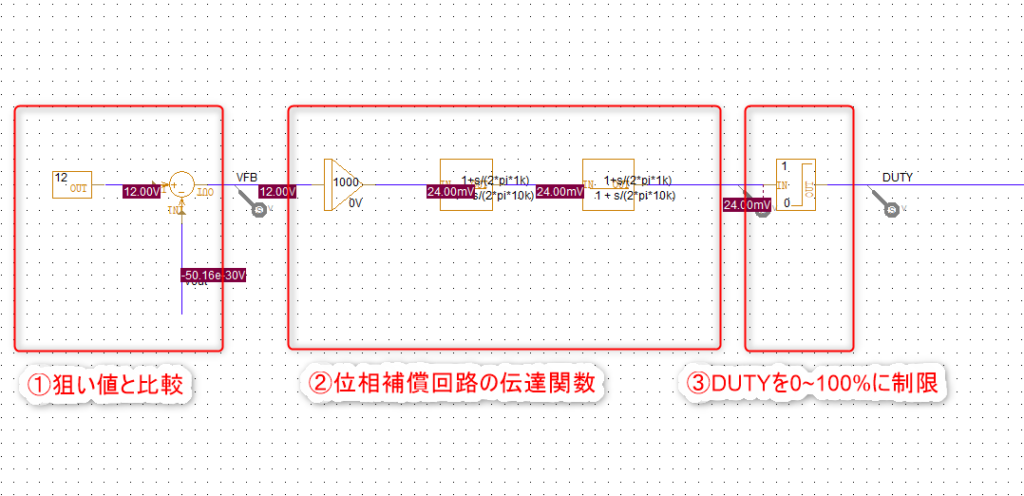

フィードバック制御部

今回の肝です。

ここでやっていることは

- 出力電圧の狙い値(12V)と出力電圧の差を計算してVFB(FeedBack)を出力する。

- 位相補償回路の伝達関数にフィードバック電圧VFBを突っ込んでDUTYを計算する。

- DUTY幅は0%~100%までなので、0~1でリミットを掛けてDUTYとして出力する。

です。

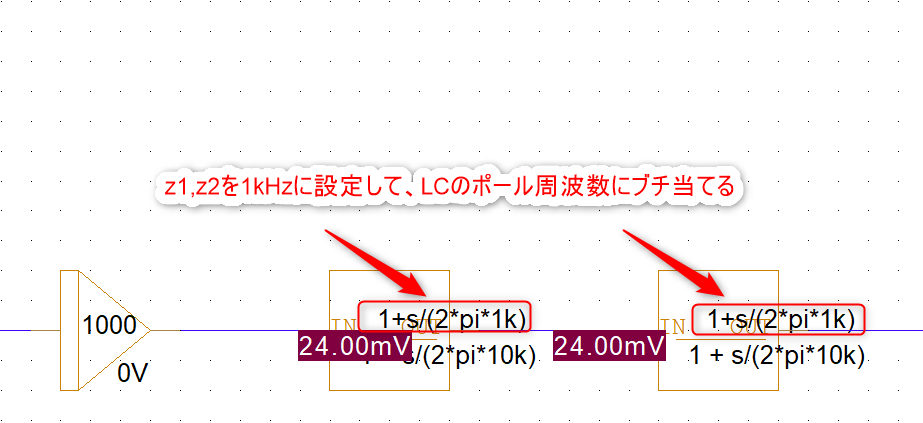

それを回路図に書き込むと、こう↓。

一番、頭を悩ませるのは位相補償回路の伝達関数ですね。

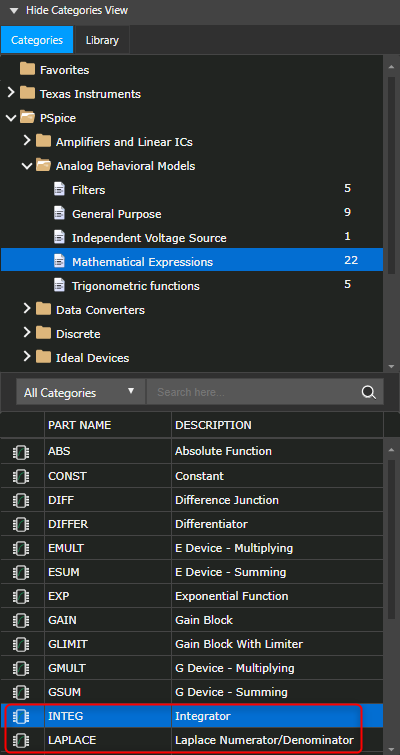

伝達関数は”LAPLACE”と”INTEG”ブロックを使って表現しています。いずれもPspice->Analog Behavioral Models->Mathematical Expressionsにあります。

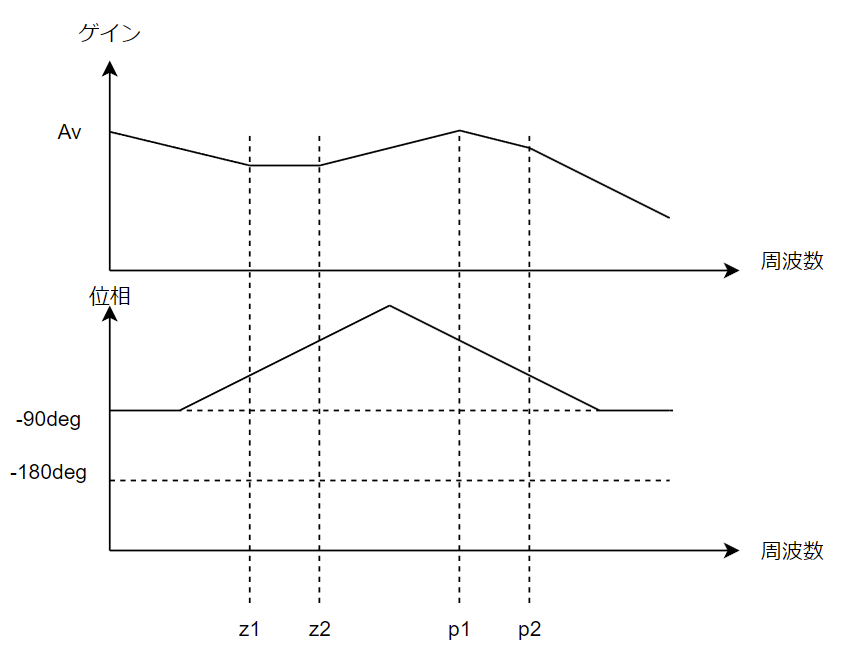

電圧モード制御の伝達関数は一般的に以下のようになります。

$$G_c(s)=\frac{Ao}{s}\frac{1+\frac{s}{ω_{z1}}}{1+\frac{s}{ω_{p1}}}\frac{1+\frac{s}{ω_{z2}}}{1+\frac{s}{ω_{p2}}}$$

これはタイプ3補償器とか言います。3pole-2zeroとも言います。3個ポールがあって、2個ゼロがあるからですね。

この位相補償器のボード線図を描くとこんな感じです↓。

1/sで低域から-20dB/decでゲインが落ちて、z1とz2でバキバキっと上がっていって、p1,p2でバキバキっと落ちていく。って感じですね。

電圧モード制御の設定の考え方を簡単に言うとこんな感じです↓。

・出力のLCで作られる2次ポールにz1,z2をブチ当ててキャンセルを狙う。

・ボード線図がいい感じになる様にDCゲイン(Ao)を上下させる。

・高域周波数で邪魔しないようにp1,p2を適当に入れて、ゲインを落としきっておく。

まぁやってみましょう。

まずは出力の2次ポール周波数を計算します。LC回路の折れ点周波数は以下のように計算できます。

$$p_{plant}=\frac{1}{2\pi\sqrt{LC}}$$

LC回路は200uHと100uFなので

$$p_{plant}=\frac{1}{2\pi\sqrt{200u*100u}}=1125.4[Hz]$$

まぁ1kHzくらいですね。なので、1kHzにz1,z2を設定してLCのポールにブチ当てます。

次です。DCゲインですね。あとあと調整すればいいので、とりあえず1000としました。(つまり20log|1000|=60dBですね。)

なんでとりあえず1000なの?を何となく言語化してみます。

位相補償の最初のポール1/sの影響で20dB/decで落ちていきます。60dBくらいあったら0dBになるのは1kHzくらいですね。スイッチング周波数は10kHzなので、そっから手前で0dBに落としたいなぁって感じですね。

10kHzの少し手前からPWMの無駄時間の影響で位相が回り始めるだろうからまぁ、一旦1kHzに0dBになるように置いとくか。で1000と設定しました。

ポールは超適当でスイッチング周波数の10kHzにしました。

もっと手前でゲインは落ち切っている想定ですが、とりあえずスイッチング周波数以上で邪魔しないようにここでバキッとゲインを落としておこうという考えで置いてます。

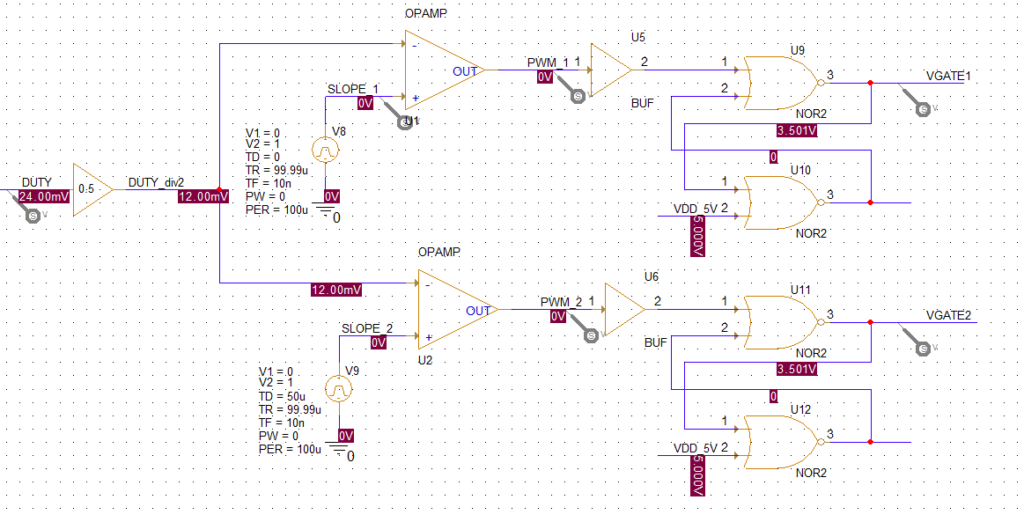

PWM波形生成部

あとは計算したDUTYをPWMに変換します。

やっていることは

- コンパレータでスロープ波形とDUTY値を比較してリセット信号をつくる。

- RS-FFを通してゲート波形をつくる。

です。

これをM1&M4とM2&M3で半周期ずつに分けてやっているって感じです。

動作波形を示した方がわかりやすいと思うので以下に示します↓。

最初の半周期はM1とM4のゲート電圧を作っています。

半周期で0V->1Vまで上がっていくSLOPE波形を作ってます(=SLOPE1)。SLOPE1とDUTYをコンパレータで比較することでリセット信号を作ってます。

そのあとRS-FFにリセットを入れることによって、リセット信号の逆論理の欲しいPWM信号を得ます。(=VGATE1)

あとの半周期でM2とM3のゲート電圧を作ってます。やってることは前半と同じです。

そうやって設定してシミュレーション回したら最初の結果が得られました。

本当に安定しているのか?は周波数解析をしないと分かりませんが、まぁスイッチングDUTYがブレブレじゃないから、まぁいいんじゃね?って思ってます。

今日はこれで以上です。

誰かの参考になれば幸いです。最後までお読みいただきありがとうございました!!!