2段オペアンプの設計方法を解説してみようという試みの記事の1回目です。

本日は2段オペアンプ回路を小信号等価回路に書き直して、DCゲインを計算しよう!

という記事です。

1回目:【2段オペアンプ設計方法】小信号等価回路化してDCゲインを計算してみる(本記事)

2回目:【2段オペアンプの設計方法】周波数特性の計算をしてみる

3回目:【2段オペアンプの設計方法】なぜ設計条件は(gm6=10gm1、Cc>0.2Cout)なのか?

小信号等価回路は回路の周波数特性を考えるのに必要です。オペアンプを設計するときに安定性を考えないといけません。そのために周波数特性を考えるんですね。

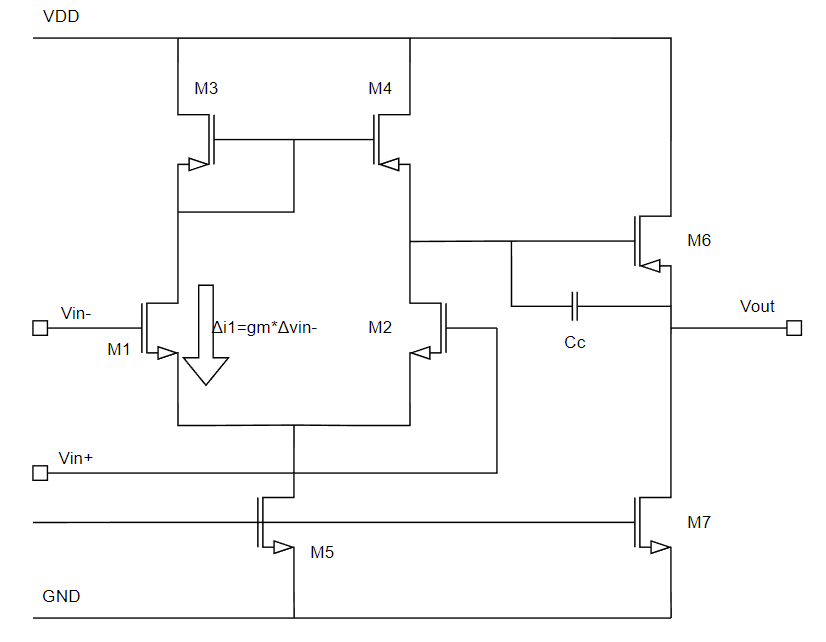

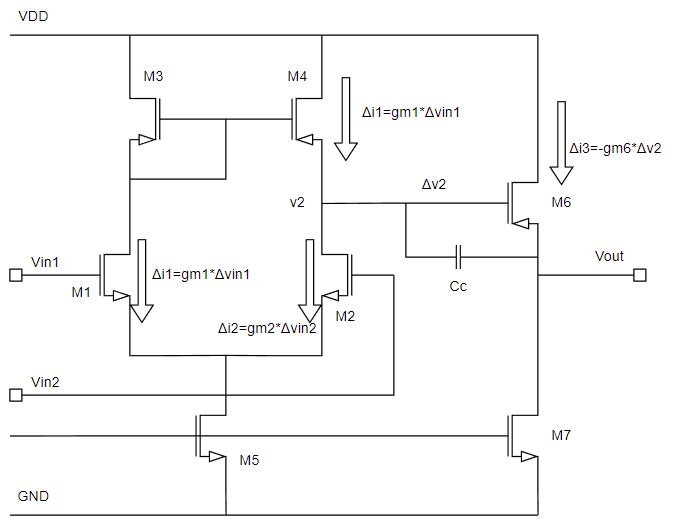

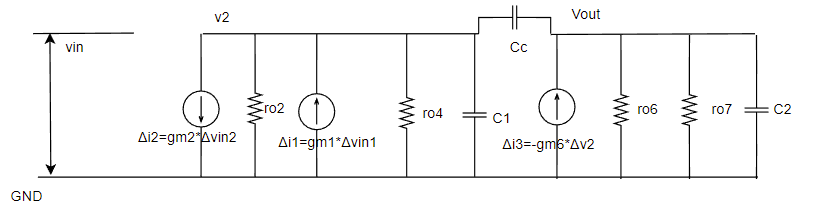

ちなみに今回考える2段オペアンプは以下の通りです↓。

2段オペアンプの設計って基礎っていうけど、むずすぎだろ。全くわからず挫折したよ。

もしくは挫折しそうだよ。

こういった悩みをお持ちの方の参考になれば幸いです。

では始めます。

動作イメージ

まずオペアンプの動作イメージをします。

vin-が変化した時を考えます。

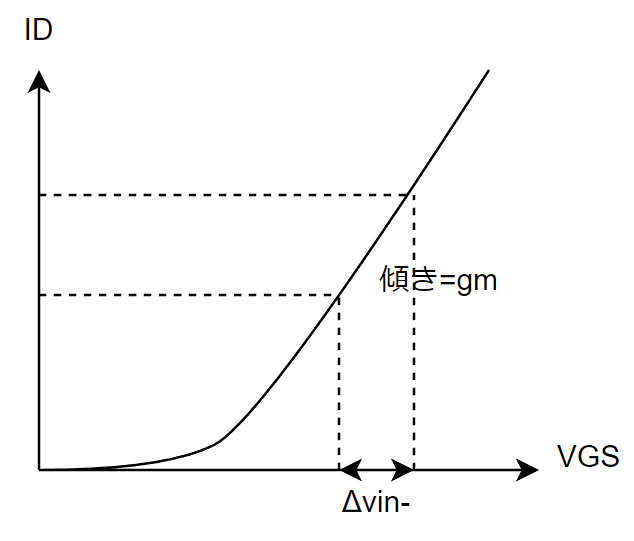

vin-=(M1のVgs)が変化するため電流がΔi1変化します。この変化量はMOSFETのgmに応じて変化します。

この増加分の電流がM3に流れます。そして、M3とM4はカレントミラーなので電流をコピーします。なので、そのままgm1*Δvin1分がM4に流れます。

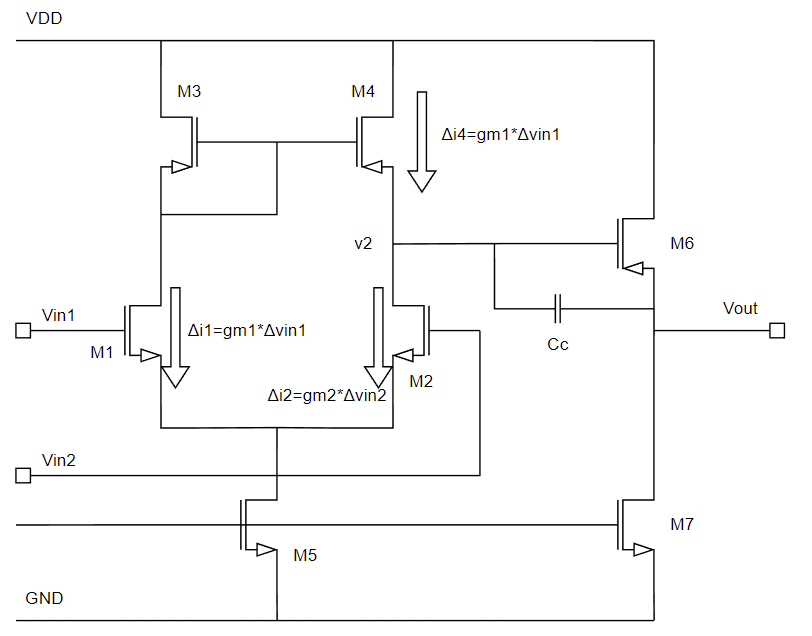

次に+側入力vin+が変化したときを考えます。M2のVgsが変化するのでΔi2変化します。これもgmに応じて増加します。

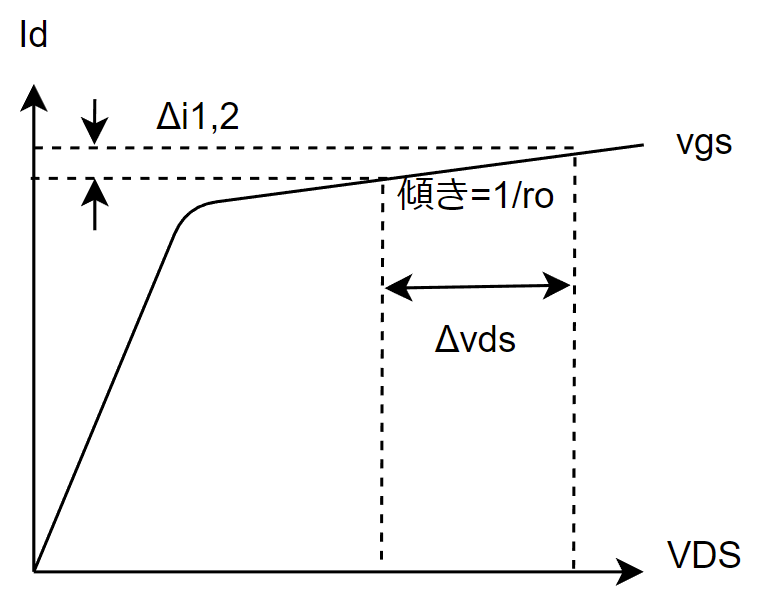

V2部分の電圧はΔi1とΔi2の変化量をM4,2のON抵抗ro4,ro2が帳尻あうように変化した電圧になります。

M6,7はソース接地回路です。V2の変化分だけM6のVgsが変化することになり、Δi3分変化します。ただしここはPMOSなので、V2が正の方向にずれたときに電流はgm6掛けた分だけ低下します。なので、”-“をつけておきます。

あとはro6,7がいい感じに帳尻合わせたところがvoutとなります。

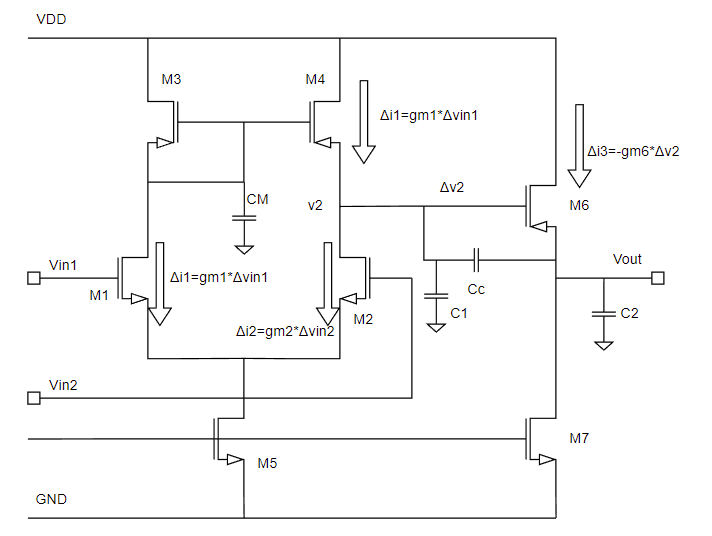

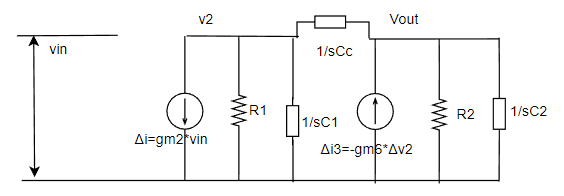

寄生容量を考慮

寄生容量を考慮すると回路図は以下のように変化します。

CM:初段のMOS M1,M2のミラー容量やM3,4のゲートゲート容量

C1:初段の出力容量

C2:2段目の出力容量

「そこに寄生容量が付くんだなぁ。」くらいの理解しか筆者はしていません(笑)

Gate-Source間、Gate-Drain間、Drain-Source間、Gate-SUB間とMOSFETには寄生容量がくっついて、”ミラー効果”によってGate-Drain間容量がゲイン倍大きく見えちゃう。

というのをふわっと頭に入れて置いて、それをひっくるめて主要な寄生容量を書くと↑のようになるんだなぁ。

という理解です。

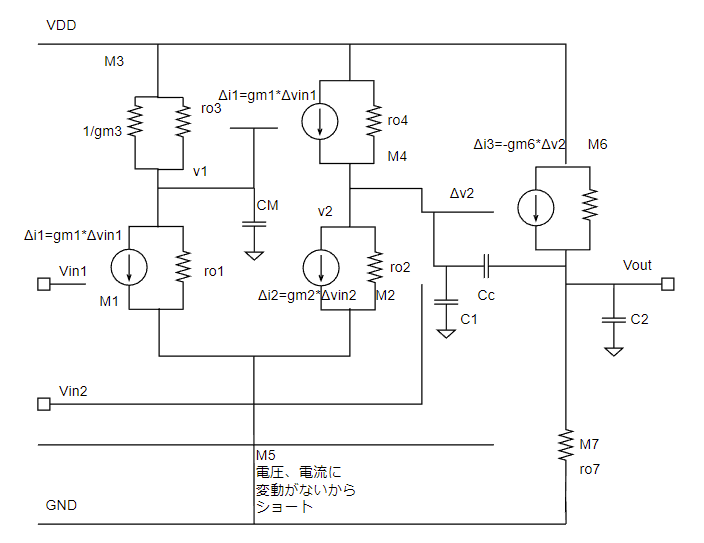

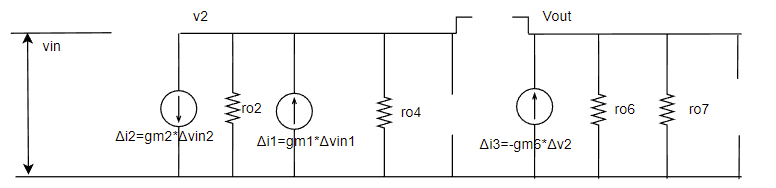

小信号等価回路化

上記の動作イメージを小信号等価回路に書き直します。

小信号等価回路にする際はMOSはON抵抗とVgsに応じて変化する定電流と見なすことが出来ます。なので、先ほどの回路を一旦以下のように書き換えます。

そんで、電源ラインとGNDラインをショートします↓。

こっからV1側は消え去ります。(なぜかは理解できていないですが、voutへ影響してこないらしいです。)

たぶん「gm3とかがデカすぎるから周波数特性のくっそ高周波数側でしか影響しないから無視」ってな感じと理解しています。

アナログ回路ってこんな風に0とみなすってのが多いからややこしいんですよね。書き換えます↓。

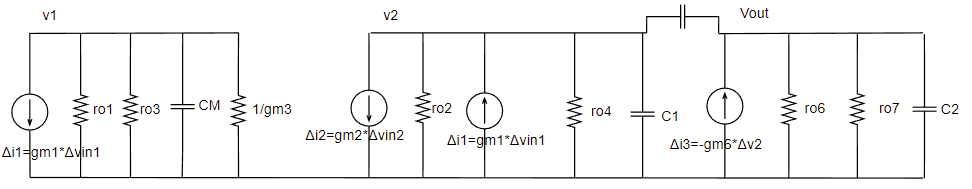

コンデンサをラプラス変換してs領域のインピーダンスに書き換えました↓。

こっから教科書とかだとro2//ro4=R1、ro6//ro7=R2として、こんな風にしてますね↓。

また、電流Δi1を下向きの矢印に変えて

Δi1+Δi2して

$$Δi1+Δi2=gm2Δvin2+(-gm1Δvin1)$$

gm2=gm1なので

$$Δi1+Δi2=gm2(Δvin2-Δvin1)$$

vin2-vin1=vinとしてgm2*vinの電流変化があったとみなしてたりしますね。

はい。小信号等価回路化は以上です。

DCゲインを計算

本来の目的は小信号等価回路から周波数特性を考えるために伝達関数を計算することなのですが、正直小信号等価回路化でお腹いっぱいなので、DCゲインだけ計算して終わりにしようと思います。

DCゲインのことを利得という人もいますね。人によって言い方が変わりますが、DCゲインとは周波数0Hz時点でのvo/vinですね。

ちょっと前の小信号等価回路を見てみます↓。

ここで周波数=0なのでs=0となります。つまりコンデンサは∞のインピーダンスとなります。つまりオープンです。

このときのV2の地点での接点方程式を立てます。

接点方程式というとなんじゃそれ?って感じですが、「入り口と出口で電流はイコールだよね。」っていうキルヒホッフの法則に従った式ですね。

$$gm1*Δvin1=gm2*Δvin2+\frac{v2}{ro2}+\frac{v2}{ro4}$$

v2でくくります↓。

$$gm1*Δvin1=gm2*Δvin2+v2(\frac{1}{ro2}+\frac{1}{ro4})$$

gm1=gm2なので、くくります↓。

$$gm1*(Δvin1-Δvin2)=v2(\frac{1}{ro2}+\frac{1}{ro4})$$

vin2-vin1=vinとします。(vin2が+入力なので。)

$$-gm1*vin=v2(\frac{1}{ro2}+\frac{1}{ro4})$$

v2/vinの形に持って行って整理します。

$$\frac{v2}{vin}=\frac{-gm1}{(\frac{1}{ro2}+\frac{1}{ro4})}$$

$$\frac{v2}{vin}=-gm1*(ro2//ro4)$$

これが1段目のDCゲインとなります。

さて、同じように2段目も式を立てます。

Voutの地点に着目して接点方程式を立てます。

$$-gm6*v2=\frac{vout}{ro6}+\frac{vout}{ro7}$$

$$-gm6*v2=vout(\frac{1}{ro6}+\frac{1}{ro7})$$

$$\frac{vout}{v2}=\frac{-gm6}{\frac{1}{ro6}+\frac{1}{ro7}}$$

$$\frac{vout}{v2}=-gm6(ro6//ro7)$$

これが2段目の利得です。

v2を消えるように1段目の利得の式を代入して、式を整理すると、

$$\frac{vout}{vin}=gm1(ro2//ro4)*gm6(ro6//ro7)$$

はい。こうなります。これが2段オペアンプのDCゲインになります。

はぁ疲れた。

今回は以上になります。次回はキャパシタを省略せずに解いてみて、どこにポールが出来るのか?だから補償コンデンサCcはこのくらいの条件にならないとダメなんだよっという設計条件を導く計算をしてみたいと思います。あー疲れた。

2段オペアンプの設計で挫折している方の参考になれば幸いです。

最後までお読みいただきありがとうございました!!