位相シフトフルブリッジコンバータ(Phase Shift Full Bridge略してPSFB)を勉強しよう!という記事の3回目です。

1回目:【電源回路】位相シフトフルブリッジコンバータの動作原理

2回目:【電源回路】位相シフトフルブリッジコンバータ(PSFB)はなぜソフトスイッチングするのか?

3回目:【電源回路】位相シフトフルブリッジコンバータ(PSFB)のデューティーサイクルロスについて(本記事)

本日は位相シフトフルブリッジコンバータのデューティーサイクルロスを解説してみようと思います。

- 位相シフトフルブリッジコンバータの動作原理を理解して、回路を動かしてみたら出力電圧がなぜか合わない。なんで?

とお悩みの方の参考になれば幸いです。

何が問題なのか?

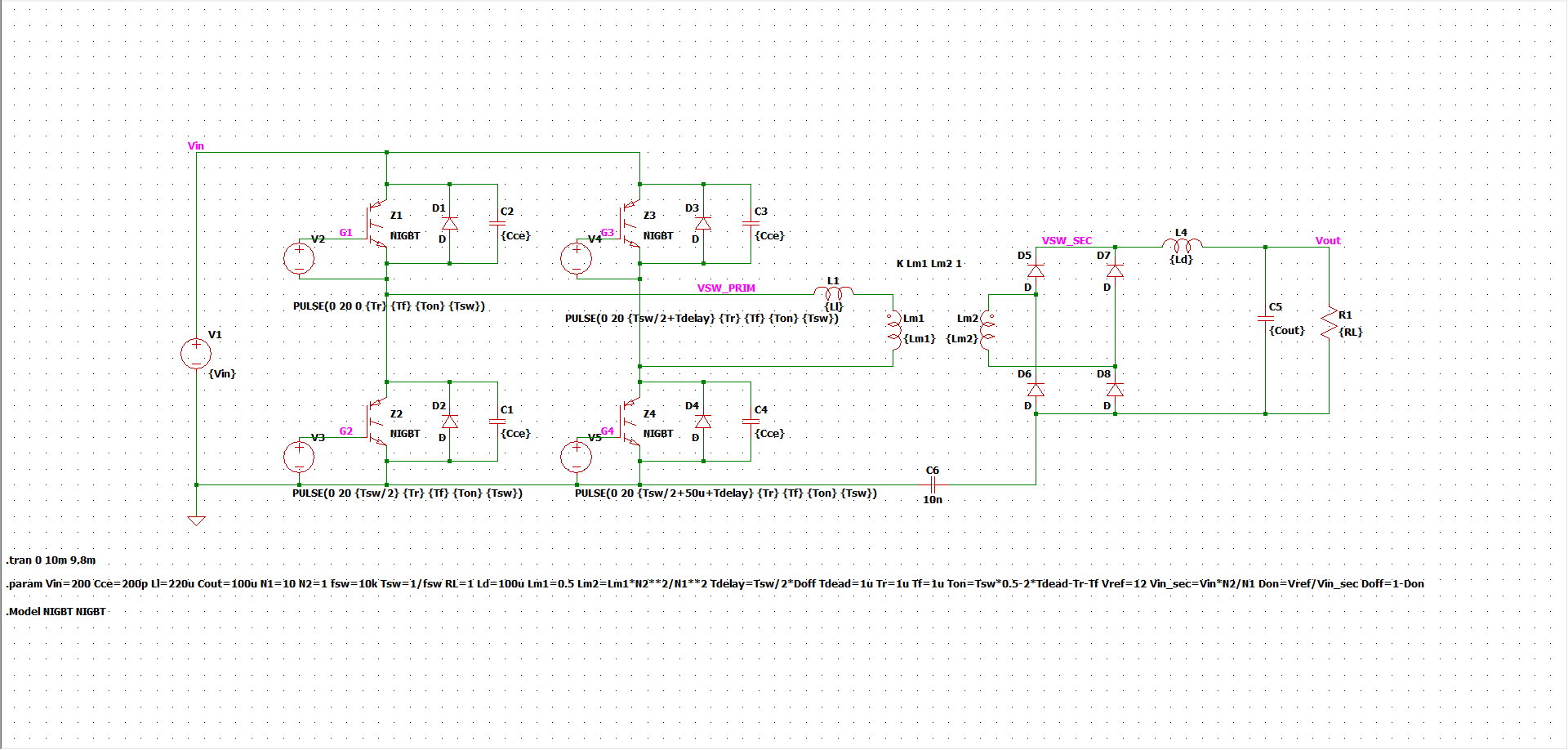

位相シフトフルブリッジコンバータを勉強したら回路動作させたくなりますよね↓。

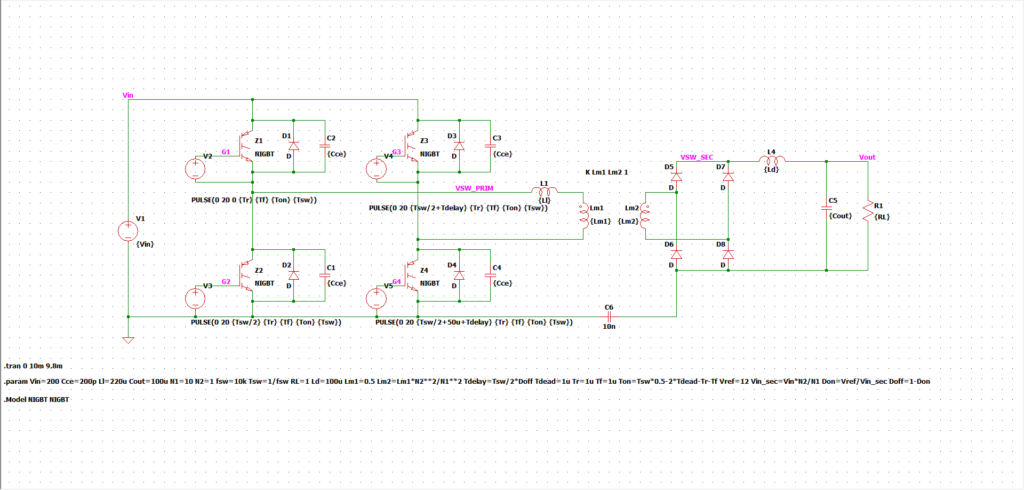

進みレグと遅れレグにディレイ入れて出力電圧を制御しようとしますよね。この式を使って↓。

$$\small{

V_{out}=\frac{n_2}{n_1}V_{in}α\\

α=\frac{V_{out}}{\frac{n_2}{n_1}V_{in}}

}$$

Vout:出力電圧[V]

Vin:入力電圧[V]

n1:変圧器の1次側巻き線数

n2:変圧器の2次側巻き線数

α:位相シフトの割合

$$\small{

α=\frac{T_1}{T_1-T_2}

}$$

T1:モード1(Q1,Q4=ONの時間)[sec]

T2:モード2(Q1,Q3=ONの時間)[sec]

このディレイ時間T2はちょっと考えて、以下の式で計算できるじゃないですか↓。

$$\small{

T_2=(1-α)\frac{T_{SW}}{2}

}$$

Tsw:スイッチング周期[sec]

例えば入力電圧200V、出力電圧12VとなるT2を計算して回路を動かしたところですね。

出力電圧が少し小さく9Vくらいが出てきます。えっなんで?

って話です。

この現象をデューディーサイクルロス言います

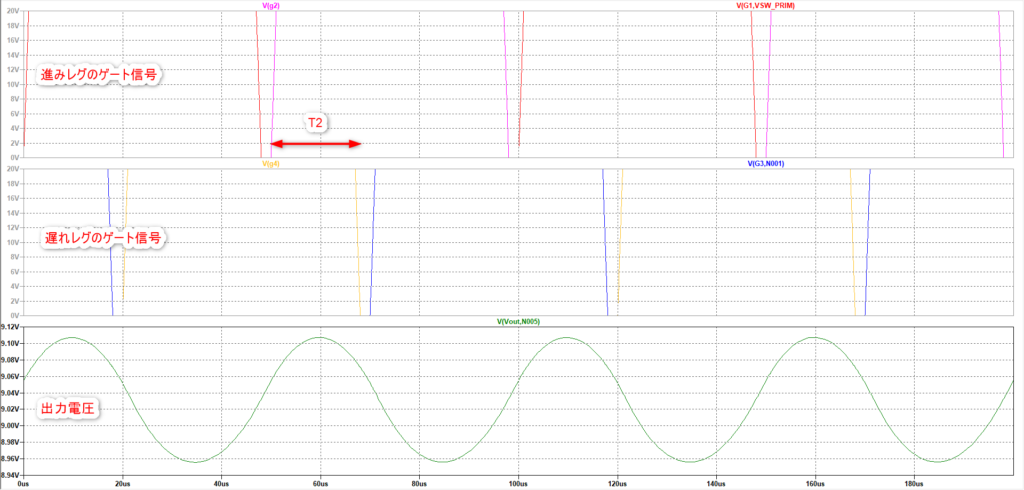

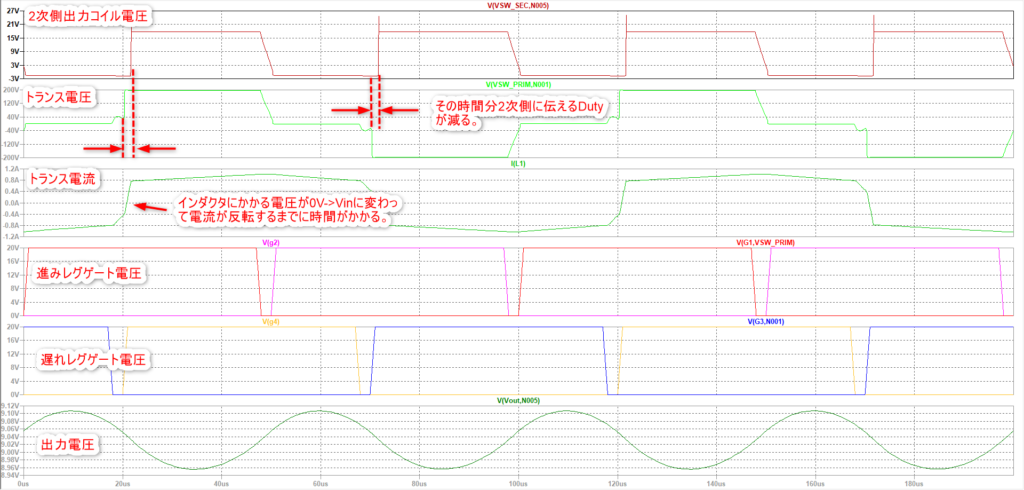

1次側の漏れインダクタンスに流れる電流を見たらわかります。

トランス1次側に「0Vが印可されるモード(モード2&モード4)」から「Vin or -Vinが印可されるモード(モード1&モード3)」に切り替わるときトランス電流は反転します。

ですが、その反転に時間がかかります。漏れインダクタンスの逆起電力の影響です。

インダクタは電流を流し続けようとします。だからゆっくり反転していくんですね。

この時間分、2次側のDuty幅が狭くなってしまって、結果的に出力電圧が想定より小さくなってしまいます。

この現象をデューティーサイクルロスと言います。

対策

単純にデューティーサイクルロス分の時間だけモード1とモード3の時間を増やしてあげれば良いです。

でもこの時間はどうやって決まっているのか?何に依存しているのか?がわからないとどれだけ増やしていいかわからないです。

このロス時間Tlossは負荷電流と漏れインダクタンスと入力電圧に依存します。

$$\small{

T_{Loss}≒2I_{out}\frac{n_2}{n_1}\frac{L_l}{V_{in}}

}$$

単純にコイルの式ですね。Ioutを1次側に変換してV=L*di/dtの式を変換している。って感じです。

なのでロス時間を小さくするためには漏れインダクタンスを小さくすれば良いです。

ですが、トレードオフとしてZVSしづらくなります。でもZVSを取ろうとするとロスがデカくて出力電圧が出せなくなる。。。というジレンマですね。

これが漏れインダクタンスを設定する条件になるって感じですね。

はい、以上で本記事は終わります。

誰かの参考になれば幸いです。最後までお読みいただきありがとうございました!!